## POWER ELECTRONICS PACKAGE MODELLING FOR ADVANCED THERMAL SIMULATIONS

**CHRISTIAN MENTIN**

**RESEARCH UNIT PACKAGING & MULTIPHYSICS**

**DIVISION POWER ELECTRONICS**

christian.mentin@silicon-austria.com

13.03.2024

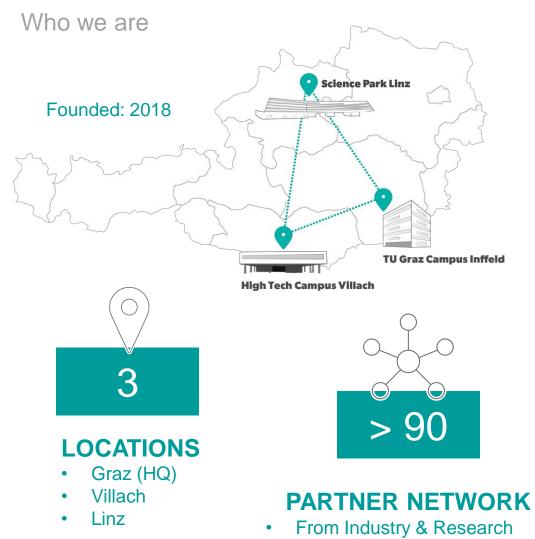

## SILICON AUSTRIA LABS (SAL)

What drives us?

As a **high-level research center** and **pioneer in EBS**, we offer the industry, access to top-class R&D infrastructures & research services to give them the decisive competitive advantage on both domestic and on international soil.

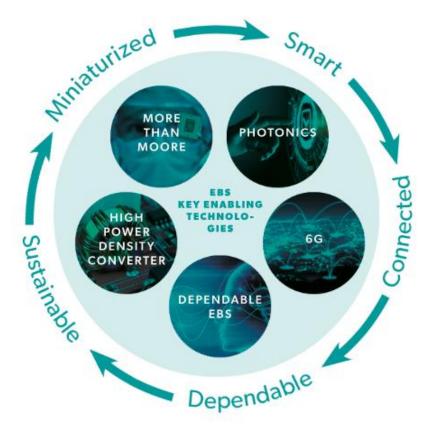

- We provide EBS Key Enabling Technologies for Smart, Connected, Dependable, Sustainable and Miniaturized Solutions

- We offer cost-effective research through the lighthouses.

More-than-Moore, Photonics, 6G, High Power Density

Converter and Dependable EBS

## **KEY FACTS\***

### **EXPERTS**

- Experienced team

- 40 nations

128

**PUBLICATIONS**

Multidisciplinary

### **PROJECT VOLUME**

• Total volume for research projects

### **SHAREHOLDER**

- 50,1 % Republic of Austria (BMK)

- 24,95 % FEEI

- 10 % Styria (SFG)

- 10 % State of Carinthia

- 4,95 % Upper Austria (UAR)

3

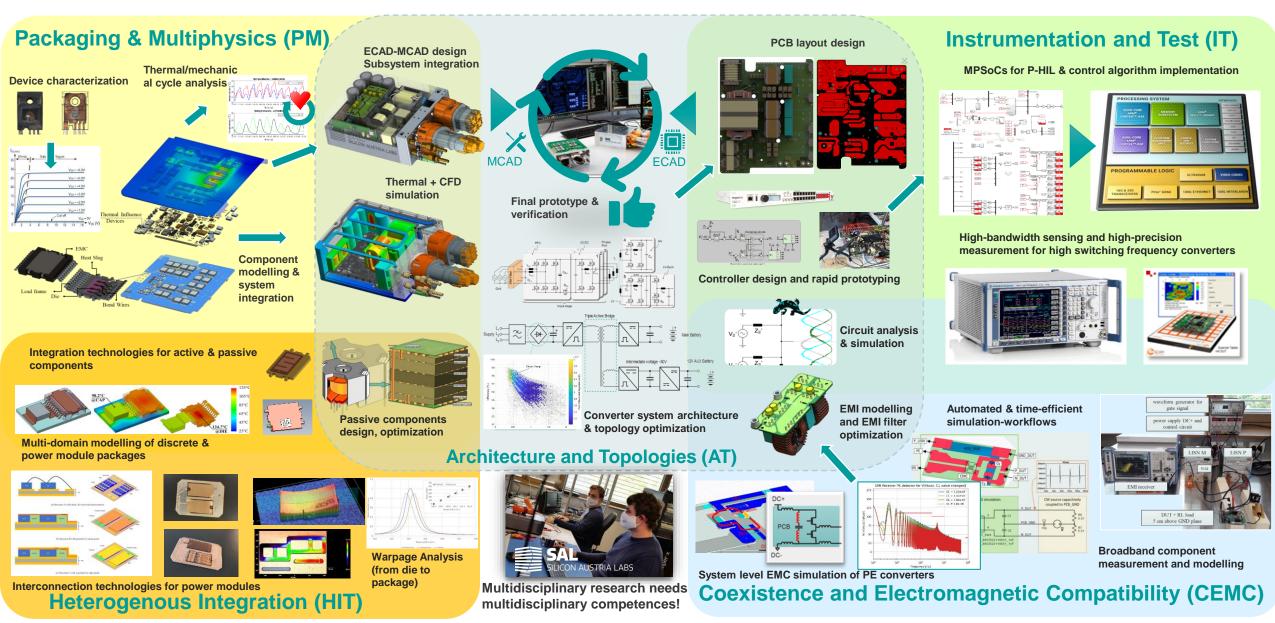

## **DIVISION POWER ELECTRONICS**

AGENDA

# 02 03 04 05

01

Motivation

Introduction

Methodology

**Simulation use-cases**

Conclusions

#### MOTIVATION

## **SIMULATION CHALLENGES**

### **MODEL-BASED DEVELOPMENT**

Silicon Austria Labs GmbH

#### MOTIVATION

## VIRTUAL POWER ELECTRONICS DEVELOPMENT

### **Concept Design**

- Specifications

- System layout

- Packaging concept

- Cooling concept

- · Component selection and design

- · Requirements review and feasibility studies

FEASIBILITY & CONCEPT

#### Virtual design validation

- Operation performance

- Cooling performance

- Scenarios

- Start-up

- Continuous/discontinuous load/derating

- Environment Conditions

### **BUT HOW TO START?**

### DESIGN VALIDATION

#### Virtualization of test procedures

- Identify most critical operation modes and routes

- Optimize reliability, operation strategy, charging, control

- Optimize for EMI

#### **Test result review**

- · Investigation of failures and deficiencies

- · Understand and improve process chain

### TESTING

Scalable models from concept phase through optimization up to the test bench simulation

AGENDA

# 01 02 03 04 05

Motivation

### Introduction

Methodology

**Simulation use-cases**

Conclusions

# THE SIMULATION USE CASE

#### INTRODUCTION

## THE BEGINNING

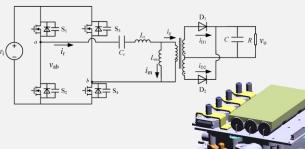

.: Coupled Thermal + Simulink (Control) + Electrical Simulations

#### INTRODUCTION

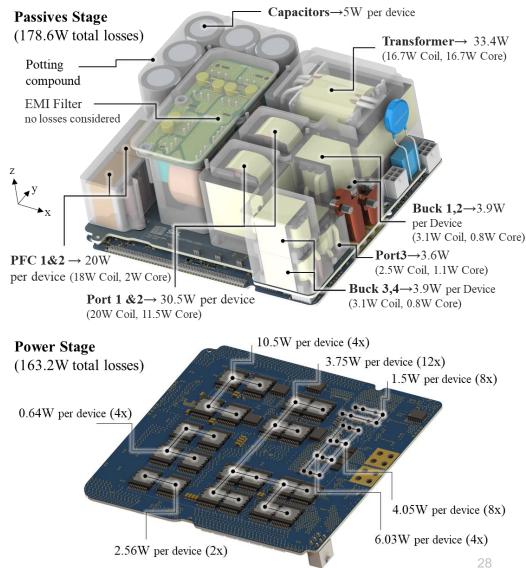

## **MAIN OBC ASSEMBLY**

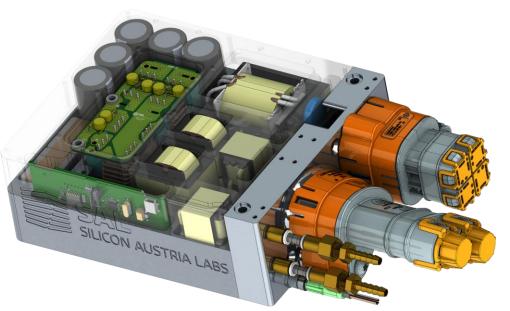

Figure 1 – Transparent Tiny Power Box assembly

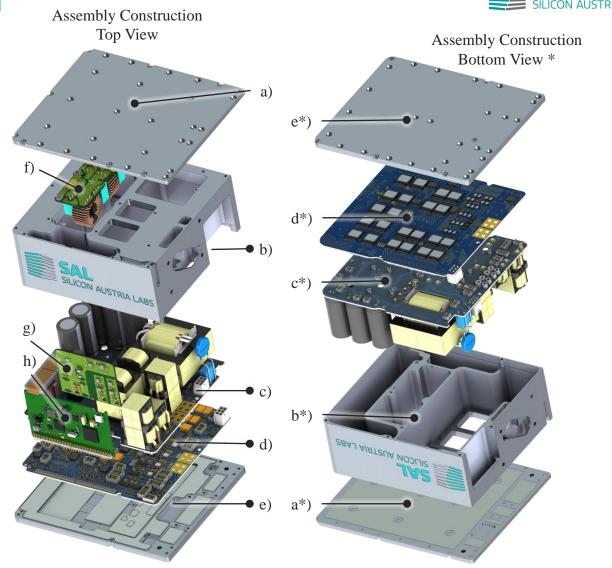

**Fig.2** Overall assembly concept with integrated liquid cooling for an automotive OBC application. The sytem setup includes a) top side cooling system, b) aluminum housing which is filled with potting material, c) passive components PCB, d) power stage PCB, e) bottom side cooling system thermal interface material, g) auxiliary supply board, h) control board, f) EMI filter board. The potting material (not shown) help to increase the heat transfer towards the liquid cooling system and improve cooling of the components. Thermal interface materials are used to thermally attach the coldplates to the semiconductors the aluminum housing.

Figure 2 – Overall assembly concept

#### Silicon Austria Labs GmbH

# OBC POTTING FOR OPTIMUM COOLING

Potting of the passive components provides proper thermal management.

Aluminum walls provide mechanical stability and transport the heat effective towards the cooling system.

Aluminum housing geometry and potting is optimized for thermal heat transfer. Figure 3 – Potting Chambers and Aluminum housing wall structures

## SIMULATION EXPERTS SURVEY

A few years ago, one of our partners conducted an internal and external survey, one of the questions being:

"How simulation engineers distribute their time when working in projects?"

About 60% of the time is consumed in data handling and preparation.

This is just one of the reasons why we are focusing on developing seamless workflows.

In a nutshell the developed tools and workflows **enable simulation team to concentrate on their work** instead of dealing with data exchange and compatibility issues.

INTRODUCTION

AGENDA

Motivation

01

02

03

04

05

Introduction

Methodology

**Simulation use-cases**

Conclusions

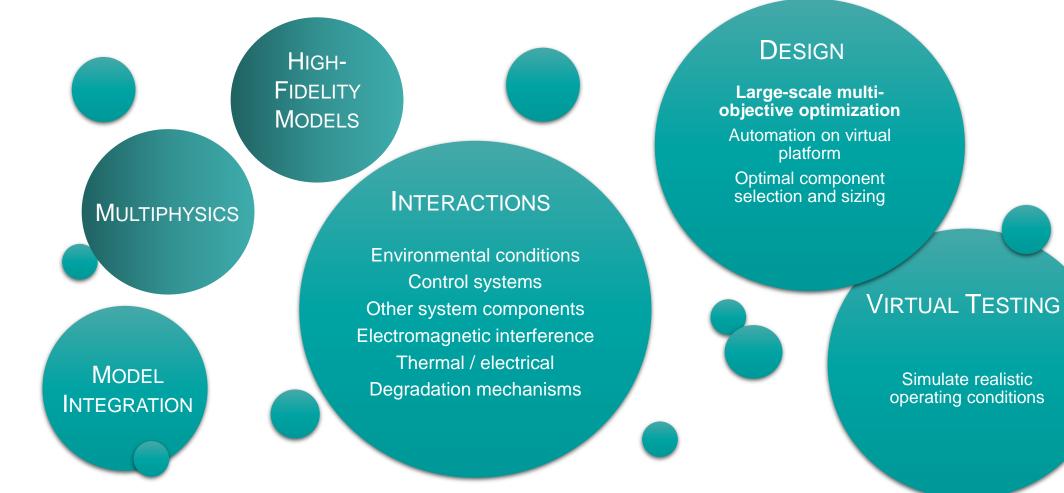

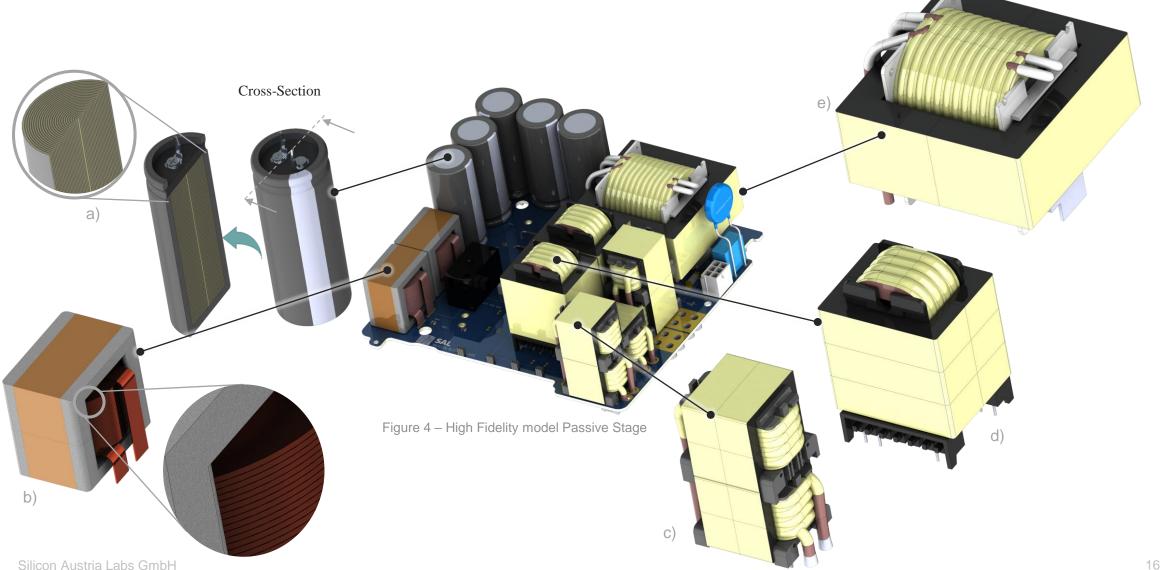

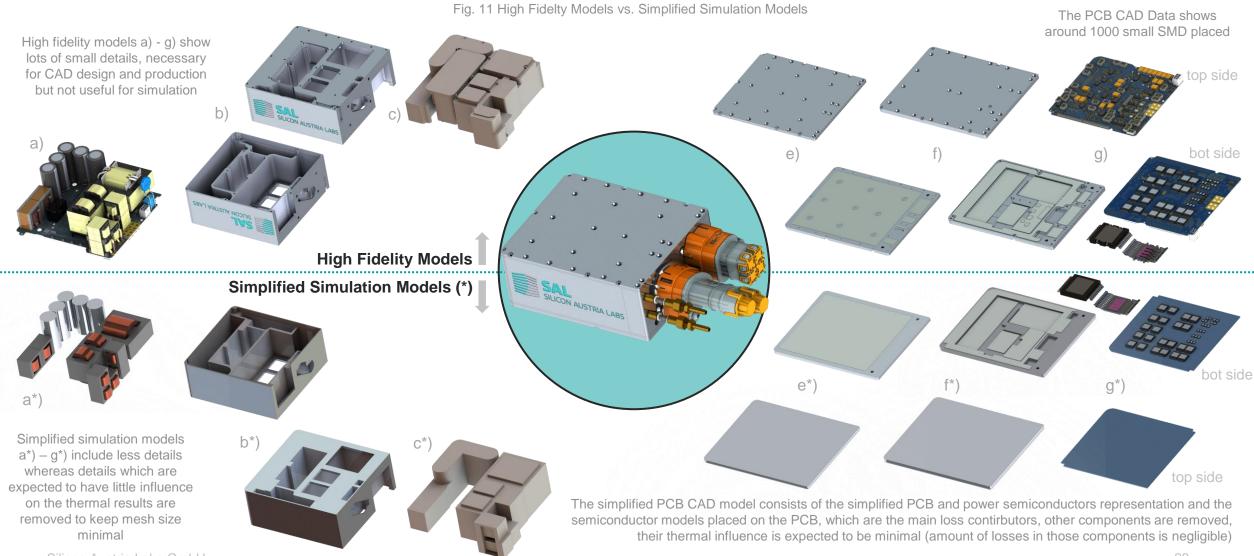

## **HIGH FIDELITY SYSTEM MODELLING**

METHODOLOGY

METHODOLOGY

## **HIGH FIDELITY SYSTEM MODELLING**

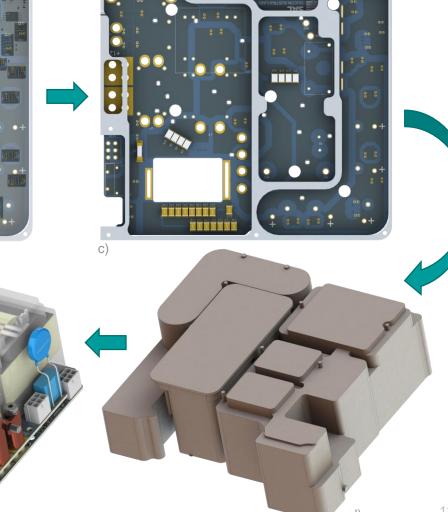

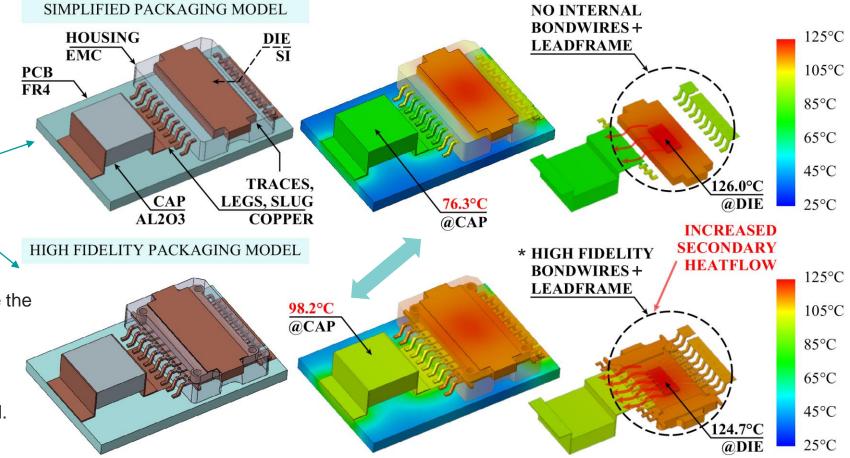

High fidelity component models are an enabler for Package model including high density system integration and accurate multi-domain simulations. structures as bondwires, die size and accurate leadframe geometry PC Real D CAD Figure 7 – High Fidelity semiconductor models generated Figure 6 - Internal Structure of Figure 5 – High Fidelity model of the by device package inspection PCB with all components placed Power Stage PCB showing top

copper layer with vias, traces and power devices.

Silicon Austria Labs GmbH

a) top View and b) bottom View

(SAL inhouse process)

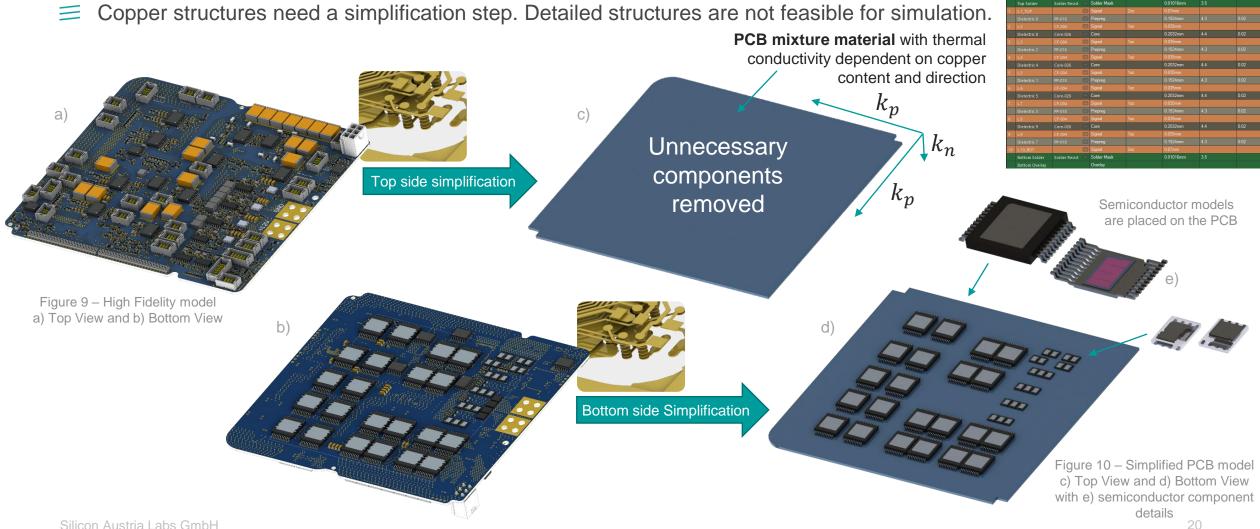

### METHODOLOGY PCB COPPER STRUCTURE Internal copper structures

- $\equiv$  Copper structures of a PCB:

- $\equiv$  Power stage PCB has 8 copper layers.

Figure 8 – High fidelity internal structures of the power stage PCB

### **SIMPLIFICATION OF PACKAGE DETAILS**

**METHODOLOGY**

## **PCB COPPER STRUCTURE** SIMPLIFICATION

PCB layer stackup (copper and dielectric layers)

# CUT VIEW

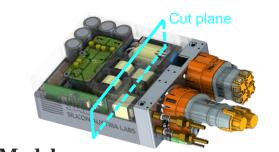

- $\equiv$  Cut view of the Tiny Power Box OBC model.

- Lots of connectors and distance holders are used as support structures. In combination with the aluminum housing this results in a mechanically stiff setup providing very little possible mechanical PCB movements between supports.

# SIMPLIFICATION FOR SIMULATION

Silicon Austria Labs GmbH

AGENDA

Motivation

Introduction

Methodology

**Simulation use-cases**

Conclusions

# SIMULATION USE-CASES

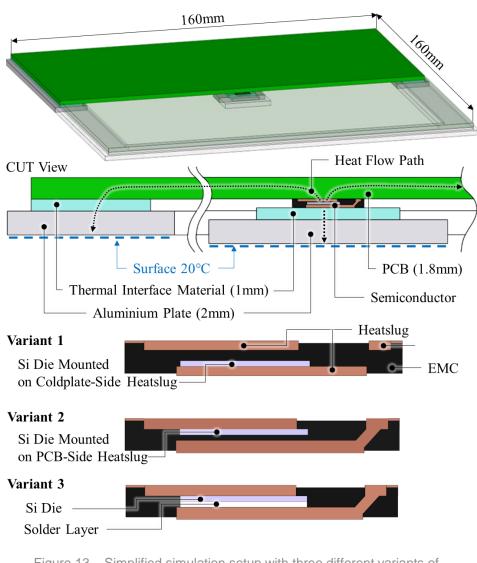

## SIMPLIFIED SIMULATION SETUP

- Mimicking a typical PCB setup with a semiconductor and heatsink

- Several variants of semiconductor models are compared.

- $\equiv$  In a later step, also the copper content in the PCB is varied.

- Since the copper content directly influences the thermal conductivity of the PCB this is taken into account with the proposed copper volume based PCB simplification approach.

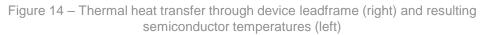

Figure 13 – Simplified simulation setup with three different variants of the (typically unknown) semiconductor packaging model.

#### SIMULATION USE CASES

Variant1

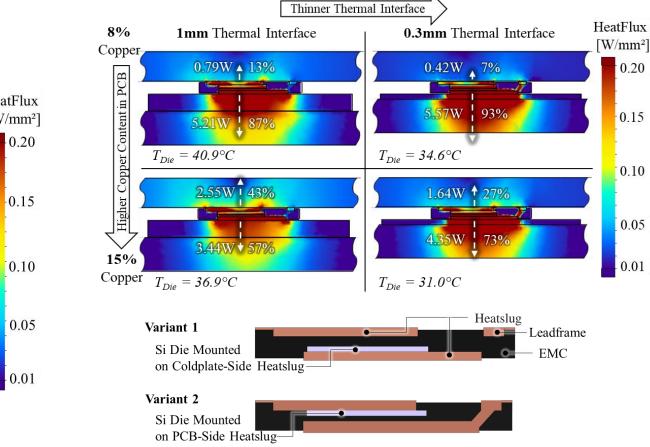

### **COMPARISON OF DIFFERENT** Figure 15 – Thermal heat transfer through device leadframe with different PCB copper **SETUPS**

SILICON AUSTRIA LABS

content and thermal interface thickness

Figure 16 – Three different variants of the semiconductor packaging model.

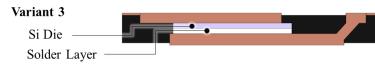

$T_{Die} = 44.1^{\circ}C$ PCB 0.98W **16**% HeatFlux Temp. **Thermal interface**  $[W/mm^2]$ [°C] 5.01W 84% **Cooling system** 48 44 Variant 2  $T_{Die} = 46.5^{\circ}C$ 4.28W 71% 40 36 1.72W 29% 32 Variant 3 28  $T_{Die} = 36.9^{\circ}C$ 2.55W24 20 3.44W + 57%

Silicon Austria Labs GmbH

# SIMULATION USE-CASES

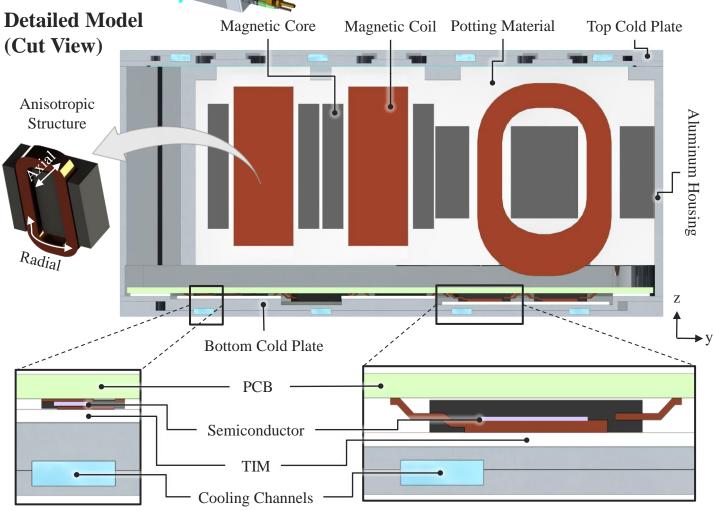

### SIMULATION RESULTS **BOUNDARY CONDITIONS**

- Loss estimates for components known from electrical simulations:

- Loss in semiconductors distributed to **semiconductor die**,

- Loss in magnetics distributed to **ferrite core** and **winding**.

| Material                    | Thermal Conductivity<br>[W/(m K)] |               |

|-----------------------------|-----------------------------------|---------------|

|                             | Radial                            | Axial         |

| Silicon (Si-die)            | 148                               |               |

| Silicon Carbide (SiC-die)   | 490                               |               |

| Epoxy mold compund (EMC)    | 0.881                             |               |

| Copper (Heat Slug)          | 384                               |               |

| Copper (Winding)            | 380                               | 10            |

| Aluminium 6063              | 190                               |               |

| Ferrite                     | 4                                 |               |

| PCB (FR4 + Copper)          | 56 (k <sub>p</sub> )              | 0.286 $(k_n)$ |

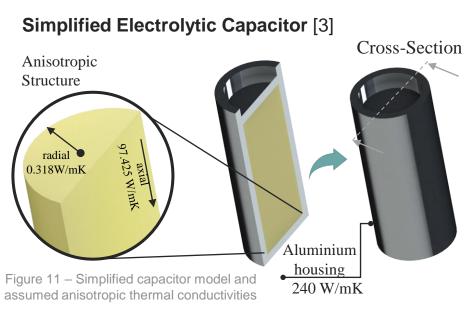

| Capacitor Winding           | 0.318                             | 97.42         |

| Capacitor Aluminium Housing | 240                               |               |

| TIM (TG-A 1250)             | 12.5                              |               |

| Conductive Tape             | 0.7                               |               |

| Potting (TCR-L-PU-2C-LV-AR) | 2.1                               |               |

| Solder layer (SnAgCu)       | 60                                |               |

TABLE II MATERIAL PROPERTIES USED FOR SIMULATIONS

#### Silicon Austria Labs GmbH

**Cooling Channel Layout in First Prototype**

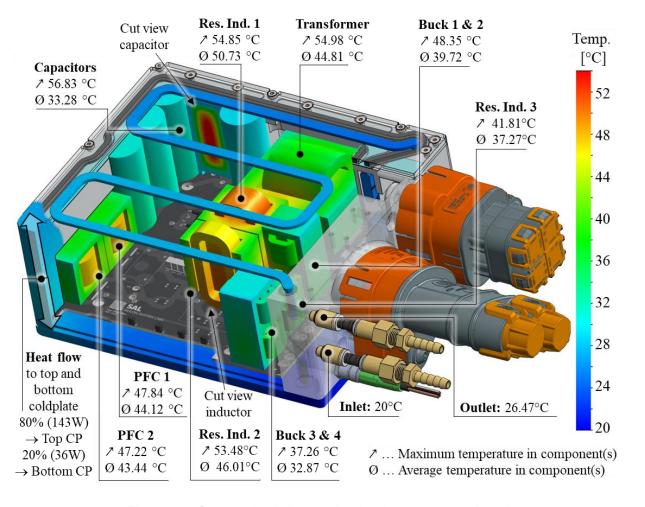

SIMULATION RESULTS **FULL SYSTEM SIMULATION**

25.62°C (-0.62°C) Die Average 26.24°C Die Average [°C] Die Average 45.30°C (+0.64°C) Die Average 44.66°C Die Average 48 Die Average 32.42°C 32.10°C (-0.31°C) 46.78°C (+1.70°C) 45.08°C 44 40 25.03°C • Inlet 25.67°C Inlet 20°C (-0.64°C) 20°C 36 32 Outlet Outlet 26.47°C 26.47°C 28 **PCB** Volume PCB Volume Avg 29.47°C (+1.59°C) Avg 27.88°C 24 Max 47.08°C (+1.62°C) Max 45.46°C <u>23.7</u>7°С 20 23.77°C

**Rerouted Cooling Channel Layout** (Reference)

Figure 18 - Comparison of thermal simulation results for two cooling channel layouts and full-system to single-PCB simulation. The cooling channels are shown as a transparent layer on top of the PCB. In general a proper cooling channel layout can achieve lower die temperatures.

### SILICON AUSTRIA LABS

Temp.

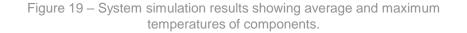

# FULL SYSTEM SIMULATION

- There is a significant amount of heat flow (36W, 20%) from the top side components transferred towards the bottom side cooling system.

- This leads to higher temperatures on the bottom side of the setup (semiconductors and PCB)

- Additionally the temperatures of the passives stage are lower since the bottom cold plate is accounted

- The water channel geometry cannot just only be adopted, also there may be an advancement by changing in-and outlet, in case the cool inlet water can reach the hottest components first.

AGENDA

Motivation

Introduction

Methodology

**Simulation use-cases**

Conclusions

#### CONCLUSIONS

### DO WE REALLY CARE ABOUT SEMICONDUCTOR PACKAGING?

\*At SAL we derive high fidelity packaging models for individual modelling of semiconductor devices.

Indeed it depends on the package...

Device models for simulation may reconstructed using:

- · Simple datasheet information or

- High fidelity package structures\*

High fidelity semiconductor models influence the heat propagation into their surroundings.

*Thermo-sensitive* electrical parameters of closely placed passive components can be influenced by the semiconductor model used.

Figure 20 - Datasheet semiconductor device model simulation results (top) compared with high fidelity model with accurate leadframe and bond wire structures (bottom)

#### Silicon Austria Labs GmbH

# SIMULATION ASPECTS

**When do we need proper package models for system simulation?**

- $\equiv$  As soon as the density on the substrate or PCB gets higher, the thermal interactions between components start to increase.

- Thermal interactions in between the system components can be observed:

- Often housing (package) parts thermally couple the different sections in an electronic assembly -> the heat flux of different stages interferes -> the system packaging design actively can control the direction of the heat flux and prevent thermal cross-talk.

- Electrical accurate component models (active and passive components) can be influenced by thermal cross-talk thereof they need proper temperature input.

CONSIDERATION OF THERMAL CROSS-TALK IS ESSENTIAL !

## REFERENCES

[1] C. Mentin, I. Recepi and P. Matzick, "Tiny Power Box - Thermal Investigations for Very High Power Density Onboard Chargers," 2022 28th International Workshop on Thermal Investigations of ICs and Systems (THERMINIC), Dublin, Ireland, 2022, pp. 1-6, doi: 10.1109/THERMINIC57263.2022.9950663.

[2] C. Mentin, I. Recepi and T. Polom, "High Fidelity Package Simulation Models Capturing Accurate Thermal Cross-Coupling," 2020 26th International Workshop on Thermal Investigations of ICs and Systems (THERMINIC), Berlin, Germany, 2020, pp. 97-103, doi: 10.1109/THERMINIC49743.2020.9420498.

[3] T. Langbauer, C. Mentin, M. Rindler, F. Vollmaier, A. Connaughton and K. Krischan, "Closing the Loop between Circuit and Thermal Simulation: A System Level Co-Simulation for Loss Related Electro-Thermal Interactions," 2019 25th International Workshop on Thermal Investigations of ICs and Systems (THERMINIC), Lecco, Italy, 2019, pp. 1-6, doi: 10.1109/THERMINIC.2019.8923595.

# THANKS FOR YOUR ATTENTION

WWW.SILICON-AUSTRIA-LABS.COM